计算机组成原理—指令系统、CPU

导读:计算机组成原理—中央处理器(2).五、指令系统.1.机器指令.1.1一般形式.指令由操作码和地址码构成.操作码.用来指明指令要完成的操作。操作码长度可固定,可改变.地址码.用来指出指令的源操作数的地址.四地址指令:.OP | A1 | A2 | A3 | A4 |.操作码.第一地

计算机组成原理—中央处理器(2)

五、指令系统

1.机器指令

1.1一般形式

指令由操作码和地址码构成

- 操作码

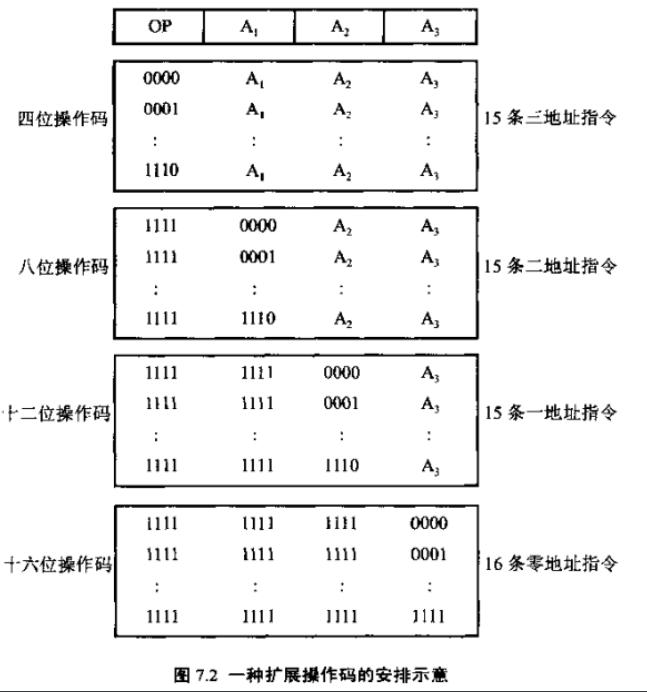

用来指明指令要完成的操作。操作码长度可固定,可改变

- 地址码

用来指出指令的源操作数的地址

四地址指令:

OP | A1 | A2 | A3 | A4 |

| 操作码 | 第一地址 | 第二地址 | 结果地址 | 下一条指令地址 |

需要4次访存

三地址指令:

| OP | A1 | A2 | A3 |

|---|---|---|---|

| 操作码 | 第一地址 | 第二地址 | 结果地址 |

因为PC地址自动+1所以不需要A4,需要4次访存

二地址指令:

| OP | A1 | A2 |

|---|---|---|

| 操作码 | 第一地址 | 第二地址 |

可将结果暂时存放到A1/A2,所以不需要A3

若结果不进入ACC(累加器)则需访存4次;反之访存3次

一地址指令 :

| OP | A1 |

|---|---|

| 操作码 | 操作码 |

其中一个操作数可在ACC中所以不需要A2

若结果进入ACC则需访存2次

零地址指令 :

无地址码,如,空操作,停机等

1.2指令字长(8的整数倍)

- 固定:等于存储字长

- 可变:按字节的整数倍变

2.操作数类型和操作类型

2.1操作数类型

地址,数字,字符,逻辑数据(逻辑运算)

2.2操作类型

数据传送(交换源:参与操作;目的:参与+结果),算术逻辑操作,移位,转移(包括有条件,无条件…)

3.寻址方式

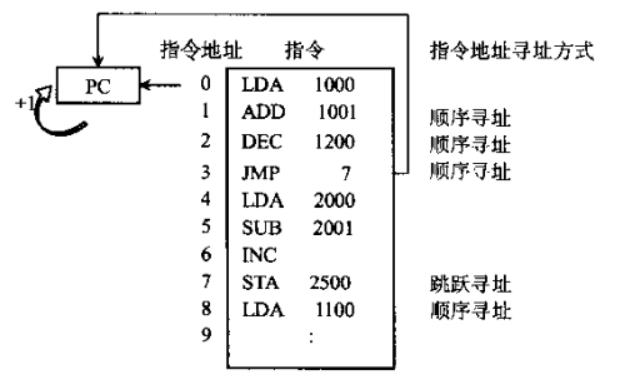

3.1指令寻址

分为顺序和跳跃两种,比较简单,见下图即可

3.2数据寻址

确定操作数的地址

- 立即寻址:操作数本身就是操作数,也叫做立即数。不需要访存

- 直接寻址:指令中的地址就是真实的地址。有效地址由地址直接给出,需要一次访存,A的位数决定了该指令操作数的寻址范围

- 隐含寻址:不需要明显给出操作数地址,一般ACC采用

- 间接寻址:有效地址由形式地址间接提供,一次间接,两次访存

- 寄存器寻址:有效地址为寄存器编号,不需要访存

- 寄存器间接寻址:有效地址在寄存器中,数据还是存在存储器中

- 基址寻址

- 变址寻址

- 相对寻址:A是相对于当前指令的偏移量

- 堆栈寻址:栈顶是低地址。

在进行设计时注意进位问题

六、CPU的结构和功能

1.CPU的结构

1.1CPU的功能

- 控制器功能:取指令,分析指令,执行指令,控制程序的输入和运算结果的输出,对总线的管理和异常、特殊情况的处理

- 运算器的功能:实现算术逻辑运算

CPU有指令控制,时间控制,操作控制,处理中断和数据加工等功能

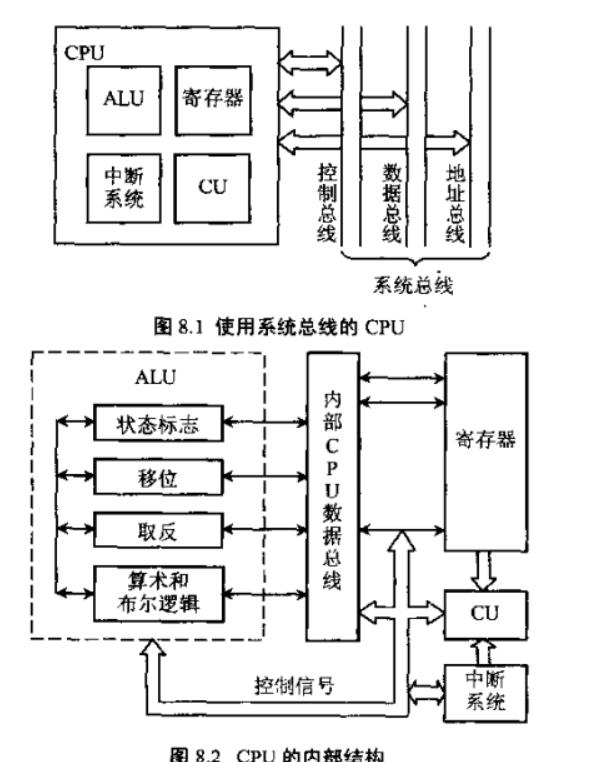

1.2CPU结构框图

控制指令:PC,IR

操作、时间控制:CU,时序电路

数据加工:ALU寄存器

处理中断:中断系统

1.3 CPU的寄存器

- 用户可见寄存器:通用寄存器,数据寄存器,地址寄存器,条件码寄存器

- 控制和状态寄存器:

不同系统的规定不同

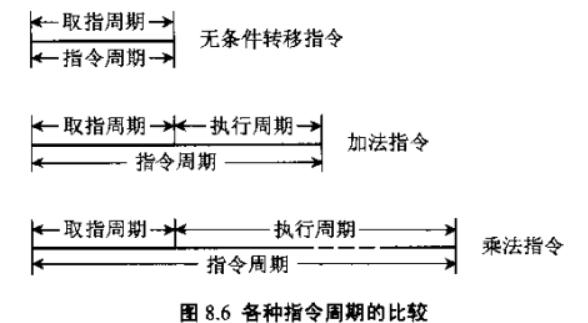

2.指令周期

2.1基本概念

CPU取出并执行一条指令所需的全部时间称为指令周期一般的,指令周期 = 取值周期 + 执行周期

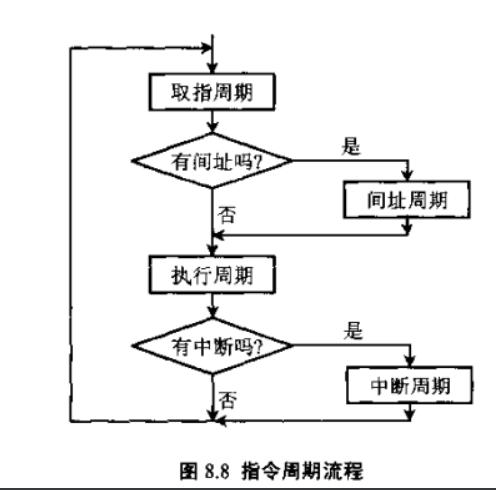

在其上的基础上,我们在加入取地址的周期和中断的周期,我们就得到了下图的一个指令周期的流程图

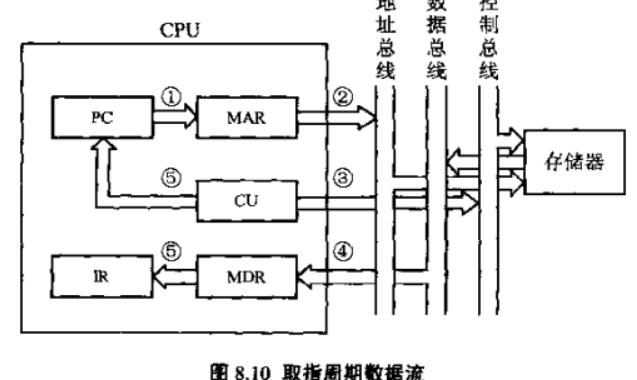

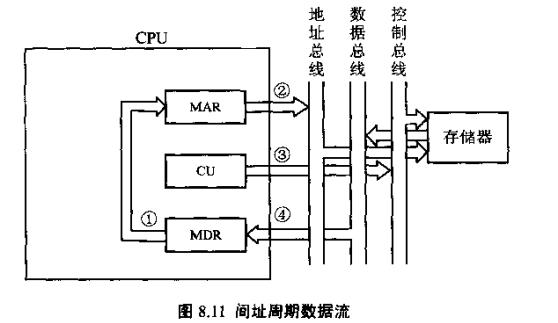

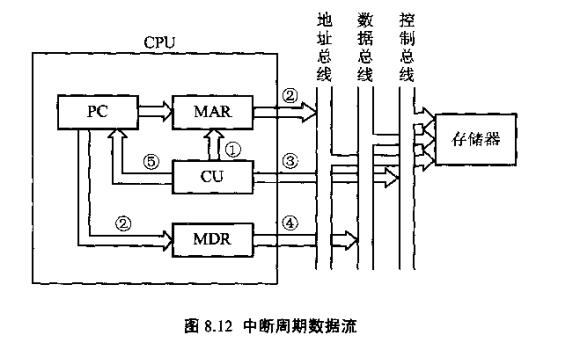

2.2指令周期数据流

- 取值周期

- 间址周期

- 执行周期:不同的指令操作不同

- 中断周期

3.指令流水

- 总结:如何提高机器速度

1.提高访存速度:高速芯片,Cache,多体并行

2.提高I/O和主机的传送速度:中断,DMA,通道,多总线,I/O处理机

3.提高运算器速度:高速芯片,改进算法,快速进位链

4.提高整机处理能力:告诉器件,改进系统结构,开发系统的并行性

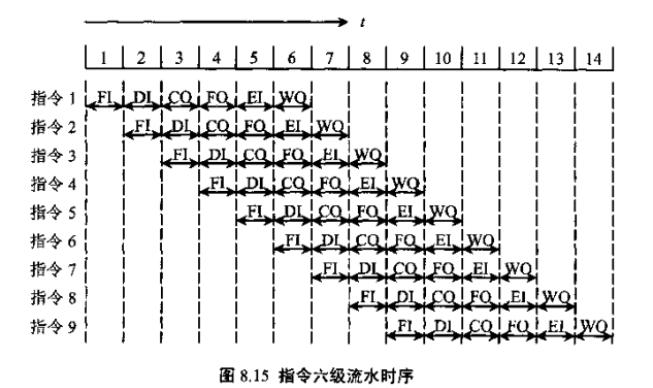

3.1指令流水原理

将每一个指令周期按照不同的指令分成若干段,实现并行操作

| FI:取指 | FO:取操作数 |

|---|---|

| DI:译码 | EI:执行指令 |

| CO:计算操作数个数 | WO:存储结果 |

3.2影响指令流水性能的因素

- 结构相关(访存冲突)

同一时间对存储器既要访问,又要取指= >暂停后再进行操作;设两个独立的存储器存放操作数和指令

- 数据相关

出现先读后写(当现代的数需要上一步的结果)= >后推法:将读指令推至写指令后;采用定向技术(旁路技术)

- 控制相关

主要由转移指令引起,使提前做的浪费= >提早预判转移的发生,提早转移

3.3流水线性能

n条指令,m级流水,每一小段时间为t

- 吞吐率:单位时间内流水线所完成指令或输出结果的数量

最大吞吐率:Tpmax = 1 / t

时间吞吐率:Tp = n / m*t+(n-1)t = Tpmax / 1+(m-1)/n

第一条指令用时m*t,其余每一个t就有一条指令结束

- 加速比:m段流水线速度与其非流水线速度的比值

Sp = (n * m * t) /m*t+(n-1)t

- 效率:各功能段的利用率

E = mnt / (mt+(n-1)t)m = Sp / m = Tp*t

上一篇:Redis为什么能抗住10万并发

下一篇:【scikit-learn基础】